TMS320C6657CZHA IC DSP FIX/FLOAT POINT 625FCBGA

Parâmetro do produto

Descrição

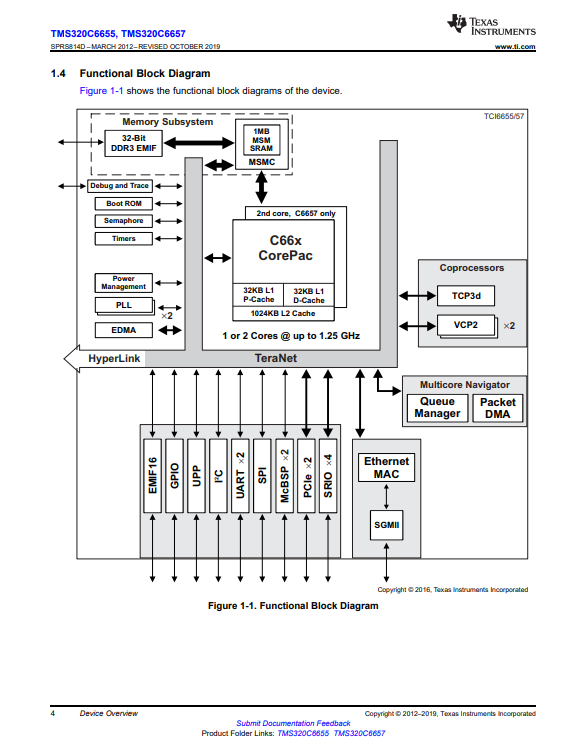

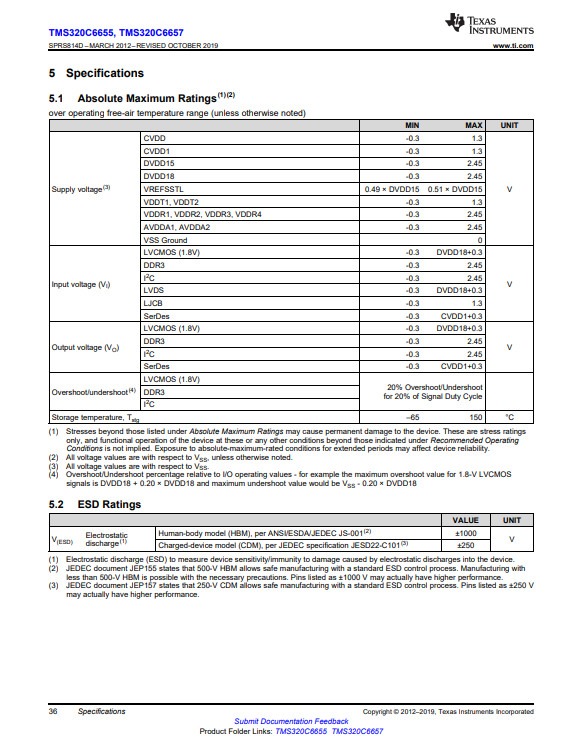

A arquitetura KeyStone da TI fornece uma plataforma programável que integra vários subsistemas (núcleos C66x, subsistema de memória, periféricos e aceleradores) e usa vários componentes e técnicas inovadoras para maximizar a comunicação intradispositivo e interdispositivo que permite que os vários recursos DSP operem de maneira eficiente e contínua.No centro dessa arquitetura estão os principais componentes, como o Multicore Navigator, que permite o gerenciamento eficiente de dados entre os vários componentes do dispositivo.O TeraNet é uma estrutura de comutação sem bloqueio que permite a movimentação de dados internos rápida e sem contenção.O controlador de memória compartilhada multicore permite o acesso direto à memória compartilhada e externa, sem consumir a capacidade da estrutura do switch.Para uso de ponto fixo, o núcleo C66x tem 4 vezes a capacidade de acumulação múltipla (MAC) dos núcleos C64x+.Além disso, o núcleo C66x integra a capacidade de ponto flutuante e o desempenho computacional bruto por núcleo é líder de mercado de 40 GMACS por núcleo e 20 GFLOPS por núcleo (frequência operacional de 1,25 GHz).O núcleo C66x pode executar 8 operações MAC de ponto flutuante de precisão única por ciclo e pode executar operações de precisão dupla e mista e é compatível com IEEE 754.O núcleo C66x incorpora 90 novas instruções (em comparação com o núcleo C64x+) destinadas ao processamento orientado a ponto flutuante e matemática vetorial.Esses aprimoramentos geram melhorias de desempenho consideráveis em kernels DSP populares usados em funções de processamento de sinal, matemática e aquisição de imagem.O núcleo C66x é compatível com código reverso com os núcleos DSP de ponto fixo e flutuante C6000 da geração anterior da TI, garantindo a portabilidade do software e ciclos de desenvolvimento de software reduzidos para aplicativos que migram para hardware mais rápido.O C665x DSP integra uma grande quantidade de memória on-chip.Além de 32KB de programa L1 e cache de dados, 1024KB de memória dedicada podem ser configurados como RAM mapeada ou cache.O dispositivo também integra 1024 KB de memória compartilhada multicore que pode ser usada como uma SRAM L2 compartilhada e/ou SRAM L3 compartilhada.Todas as memórias L2 incorporam detecção e correção de erros.Para acesso rápido à memória externa, este dispositivo inclui uma interface de memória externa DDR-3 de 32 bits (EMIF) rodando a uma taxa de 1333 MHz e possui suporte ECC DRAM.

| Especificações: | |

| Atributo | Valor |

| Categoria | Circuitos Integrados (CIs) |

| Incorporado - DSP (Processadores de Sinal Digital) | |

| Mfr | Instrumentos Texas |

| Series | TMS320C66x |

| Pacote | Bandeja |

| Estado da peça | Ativo |

| Tipo | Ponto Fixo/Flutuante |

| Interface | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Taxa de Relógio | 1GHz |

| Memória não volátil | ROM (128kB) |

| RAM no chip | 2,06 MB |

| Tensão - E/S | 1,0 V, 1,5 V, 1,8 V |

| Tensão - Núcleo | 1,00V |

| Temperatura de operação | -40°C ~ 100°C (TC) |

| Tipo de montagem | Montagem em superfície |

| Pacote / Estojo | 625-BFBGA, FCBGA |

| Pacote de dispositivos do fornecedor | 625-FCBGA (21x21) |

| Número do produto base | TMS320 |

RelacionadoPRODUTOS

-

Tel

-

E-mail

-

skype

-

Whatsapp

Whatsapp